LVGL学习记录——(1)搭建PC仿真器

在没有ESP32开发板的情况下,可以使用PC仿真,来学习LVGL。

官方介绍可以使用Simulator的IDE有很多,我采用的是VSCODE+PlatformIO。PlatformIO是跨平台、跨架构、多框架的开发工具,由于我之前学习STM32时已经安装过PlatformIO插件,此处不再介绍

在没有ESP32开发板的情况下,可以使用PC仿真,来学习LVGL。

官方介绍可以使用Simulator的IDE有很多,我采用的是VSCODE+PlatformIO。PlatformIO是跨平台、跨架构、多框架的开发工具,由于我之前学习STM32时已经安装过PlatformIO插件,此处不再介绍

作为基于ARM7、Cortex-M3硬件开发的嵌入式工程师,我一直反对使用RTOS。不仅因为不恰当的使用RTOS会给项目带来额外的稳定性风险,更重要的是我认为绝大多数基于ARM7、Cortex-M3硬件的项目,还没复杂到使用RTOS的地步,使用状态机就足够了。

早期嵌入式开发没有嵌入式操作系统的概念 ,直接操作裸机,在裸机上写程序,比如用51单片机基本就没有操作系统的概念。通常把程序分为两部分:前台系统和后台系统。

本文主要讲针对STM32的UCOSIII3.03版本的文件与内核分析。此文只是对UCOSIII粗略的讲解,希望读者在读完后能对UCOSIII系统整体多些认识,细节方面还请读者参考相关书籍,如《嵌入式实时操作系统ucosiii》。介于作者水平有限,若有错误,请及时批评指正。

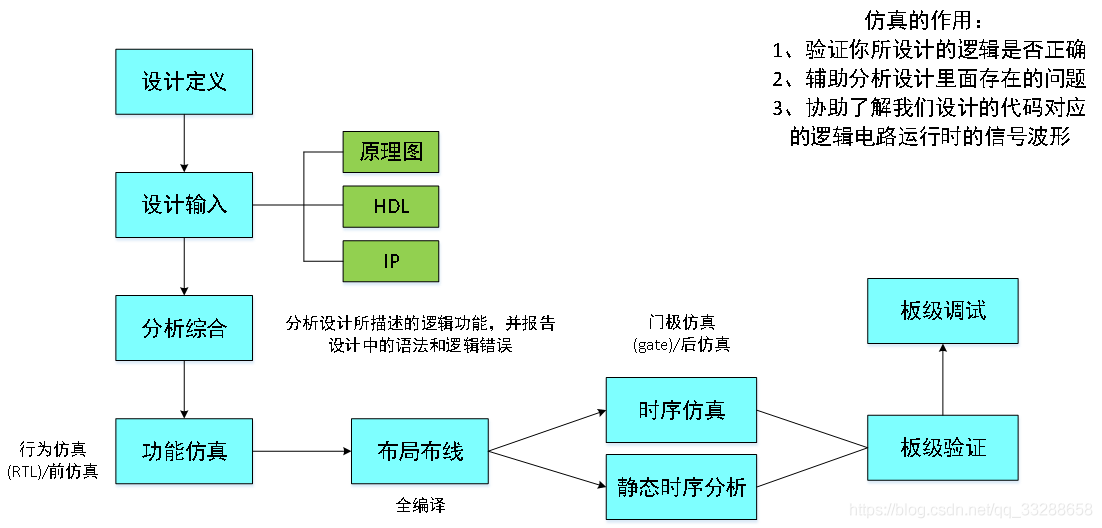

FPGA的开发遵循一定的流程,我们要学会站在巨人的肩膀上进行FPGA开发,听取前人的经验,这篇博文摘自《FPGA之道》,一起来学习下作者对于FPGA开发的丰富经验。

FPGA设计开发流程

这套开发流程无论是对于Altera还是Xilinx的开发软件都适用,要深刻理解每个步骤所代表的含义:

1.设计定义指的是我们要明确所设计的模块或系统的功能,模块划分。最好能用Visio将模块输入/输出端口、寄存器、LUT等表现出来,在设计输入中照图施工即可。

实际上就是乘加器,FPGA内部可以集成多个乘加器,而一般的DSP芯片往往每个core只有一个。换言之,FPGA可以更容易实现多个DSP core功能。在某些需要大量乘加计算的场合,往往多个乘加器并行工作的速度可以远远超过一个高速乘加器。

将全屏写入 RLE 压缩文件。

不久前,我写了另一个博客页面,关于将BMP文件导入NES屏幕工具。这里。。。

NES 屏幕工具 BMP 导入

通常,我不会将BMP导入NES屏幕工具。我发现这很困难。

tlib是一个轻便、精小的win32窗口程序框架,配合ResEdit工具来绘制图形程序的用户界面,仅仅通过少量的代码来实现对图形界面的控制

使用ResEdit新建一个Resource script(*.rc)工程,并绘制一个窗口界面,保存文件为resource.res

了解过去,我们才能知其然,更知所 以然。总结过去,我们才会知道我们明天该如何去规划,该如何去走。在时间的滚轮中,许许多的东西就像流星一样一闪而逝,而有些东西却能经受着时间的考验散 发着经久的魅力,让人津津乐道,流传至今。要知道明天怎么去选择,怎么去做,不是盲目地跟从今天各种各样琳琅满目前沿技术,而应该是去 —— 认认真真地 了解和回顾历史。