I2S音频总线介绍

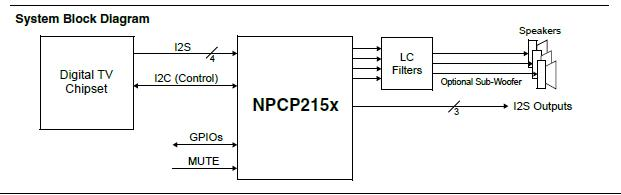

I2S(Inter-IC Sound)总线,是飞利浦公司为数字音频设备之间的音频数据传输而制定的一种总线标准,该总线专责于音频设备之间的数据传输,广泛应用于各种多媒体系统。

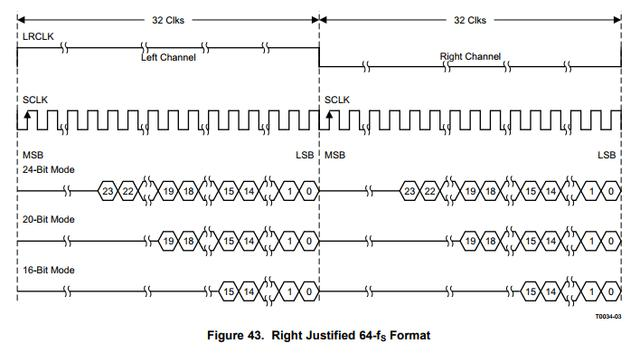

在数字音频Datasheet中,我们经常看到512FS,384FS,256FS,64FS; 32kHz,44.1kHz,48K,96K,192KHZ,384KHZ MCLK等概念。一般在数字音频芯片用4个pin作为通讯接口:BCLK(SCLK),LRCK,DOUT,MCLK。

24bit的采样,2channel, 24_2(channel)_2(每个LR有几个BCLK组成) = 96fs 按照倍数的增加,会有如下的选择: 96fs、192fs、384fs、768fs(这个级别的估计一般的ADC很难)。

其实xxxfs就是这么算出来的,也是固定的,当你定了几个channel,多少位深,就几乎可以确认是多少fs了。从主观的角度来看,fs的数值越大,那么一个完整的LRCLK越多,那承载的数据量就越大,随之的就是音质就会更加好。

从主观的角度来看,xxxfs的数值越大,那么一个完整的LRCLK越多,那承载的数据量就越大,随之的就是音质就会更加好。

现在做个总结。

-

SAMPLING RATE: 32kHz,44.1kHz,48kHz,96kHz,192HHZ等:音频采样率,越高声音质量越高。

-

256fs中“fs” 就是表示audio sampling frequency(LRCK),这里音频控制线就是通过用LRCK来实现了32kHz,44.1kHz,48kHz,96kHz的采样。ADCLRC 控制左右声道控制指示。可以想像ADCLRC的周期就是音频采样周期。这里音频芯片MCLK可以通过例如256(fs)×LRCK(KHz),得出。

-

采样率是由I2S的LRCK脚决定的,它会根据你提供的MCLK和LRCK决定是xxxfs xxx=f(MCLK)/f(LRCK)= MCLK/ Sample_rate。

-

而BCLK是与MCLK有一定的比率关系,一般情况下, BCLK=MCLK/4

-

MCLK=fs*sample_rate

例如:

1、系统要达到频率响应到40KHZ ,选择采样频率为96K,模式采用256fs,则MCLK =XXX* sample_rate =256fs*96K =24.576M

2、I2S数据:

系统选择256FS

FS( LRCK):96K

MCLK:24.576M

MCLK =XXX*FS=XXX* sample_rate =256*96K =24.576M

BCLK:6.144M

BCLK=MCLK/4=24.576/4=6.144M

3、 系统要达到频率响应到20KHZ ,选择采样频率为48K, 模式采用256fs, 则MCLK =XXXfs* sample_rate =256*48K =12.288M

4、I2S数据:

系统选择256FS

FS( LRCK):48K

MCLK =XXX*FS=XXX* sample_rate =256*48K =12.288M

BCLK=MCLK/4=12.288/4=3.072M

5、 系统要达到频率响应到20KHZ ,选择采样频率为48K, 模式采用512fs, 则MCLK =XXXfs _sample_rate =512_48K =24.576M

6、I2S数据:

系统选择512FS

FS( LRCK):48K

MCLK =XXX*FS=XXX* sample_rate =256*48K =24.576M

// BCLK=MCLK/4=12.288/4=6.144M (需要测量)

SCKI:SYSTEM CLOCK INPUT; -> MCLK

BCK: AUDIO DATA BIT CLOCK INPUT/OUTPUT; -> SCLK

LRCK: AUDIO DATA LATCH ENABLE INPUT/OUTPUT; -> LRCK或者(RFS)

DOUT: AUDIO DATA DIGITAL OUTPUT. -> SDO

IIS音频总线学习(一)数字音频技术

一、声音的基本概念

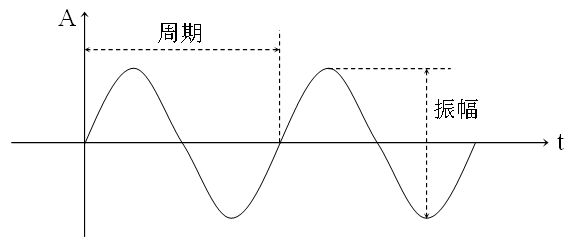

声音是通过一定介质传播的连续的波。

图1 声波

重要指标:

振幅:音量的大小

周期:重复出现的时间间隔

频率:指信号每秒钟变化的次数

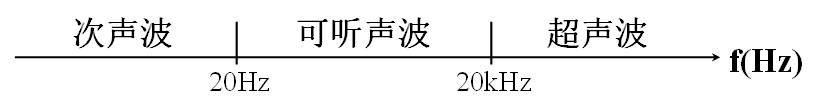

声音按频率分类:

图2 声音的频率(语音信号频率范围:300Hz-3kHz)

声音的传播携带了信息,它是人类传播信息的一种主要媒体。 声音的三种类型:

波形声音:包含了所有声音形式

语音:不仅是波形声音,而且还有丰富的语言内涵(抽象→提取特征→意义理解)

音乐:与语音相比,形式更规范。音乐是符号化的声音。

二、声音的数字化

1.声音信号的类型

模拟信号(自然界、物理)

数字信号(计算机)

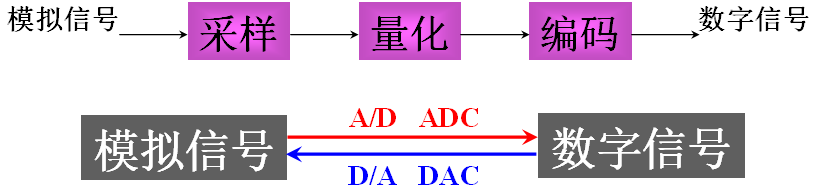

2.声音数字化过程

图3 声音数字化过程

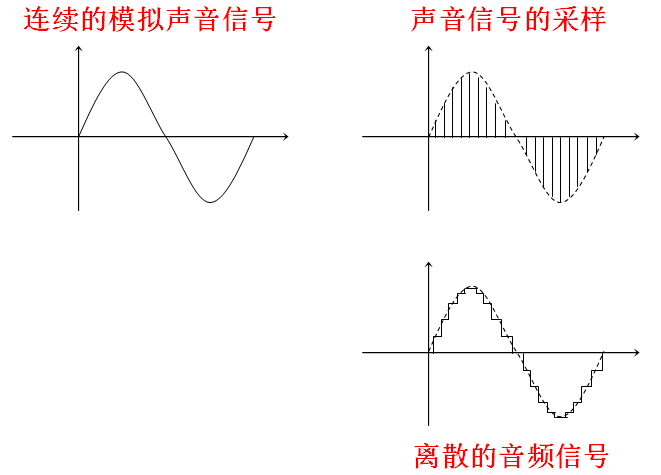

3.声音数字化过程示意图

图4 声音数字化过程示意图

4.声音数字化三要素

5.声音数字化的数据量

音频数据量=采样频率×量化位数×声道数/8(字节/秒)

三、音频的文件格式

1.WAV文件

WAV是Microsoft/IBM共同开发的PC波形文件。因未经压缩,文件数据量很大。

特点:声音层次丰富,还原音质好

2.MP3文件

MP3(MPEG Audio layer3)是一种按MPEG标准的音频压缩技术制作的音频文件。

特点:高压缩比(11:1),优美音质

3.WMA文件

WMA(Windows Media Audio)是Windows Media格式中的一个子集(音频格式)。

特点:压缩到MP3一半

4.MIDI文件

MIDI(乐器数字接口)是由一组声音或乐器符号的集合。

特点:数据量很小,缺乏重现自然音

四、数字音频压缩标准

1.音频压缩方法概述

图5

压缩编码技术是指用某种方法使数字化信息的编码率降低的技术

音频信号能压缩的基本依据:

①声音信号中存在大量的冗余度;

②人的听觉具有强音能抑制同时存在的弱音现象。

音频信号压缩编码的分类:

①无损压缩(熵编码)

霍夫曼编码、算术编码、行程编码

②有损压缩

波形编码–PCM、DPCM、ADPCM 、子带编码、矢量量化

参数编码–LPC

混合编码–MPLPC、CELP

2.音频压缩技术标准

五、声卡

1.声卡的主要功能

声卡是负责录音、播音和声音合成的一种多媒体板卡。其功能包括:

①录制、编辑和回放数字音频文件

②控制和混合各声源的音量

③记录和回放时进行压缩和解压缩

④语音合成技术(朗读文本)

⑤具有MIDI接口(乐器数字接口)

2.芯片类型

CODEC芯片(依赖CPU,价格便宜)

数字信号处理器DSP(不依赖CPU)

I2S 总线协议

一、I2S 总线概述

音响数据的采集、处理和传输是多媒体技术的重要组成部分。众多的数字音频系统已经进入消费市场,例如数字音频录音带、数字声音处理器。对于设备和生产厂家来说,标准化的信息传输结构可以提高系统的适应性。I2S(Inter—IC Sound)总线是飞利浦公司为数字音频设备之间的音频数据传输而制定的一种总线标准,该总线专责于音频设备之间的数据传输,广泛应用于各种多媒体系统。

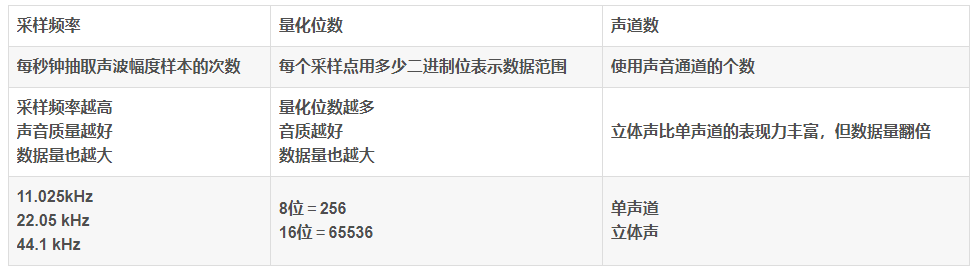

二、I2S 总线规范

I2S 总线拥有三条数据信号线:

1、SCK: (continuous serial clock) 串行时钟对应数字音频的每一位数据,SCK 都有 1 个脉冲。SCK 的频率=2×采样频率×采样位数。

2、WS: (word select) 字段(声道)选择

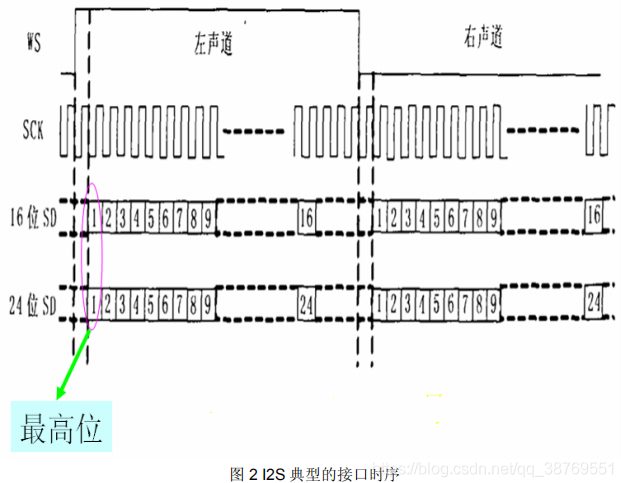

用于切换左右声道的数据。WS 的频率=采样频率。 命令选择线表明了正在被传输的声道。 WS 为“1”表示正在传输的是左声道的数据。 WS 为“0”表示正在传输的是右声道的数据。 WS 可以在串行时钟的上升沿或者下降沿发生改变,并且 WS 信号不需要一定是对称的。在从属装置端,WS 在时钟信号的上升沿发生改变。WS 总是在最高位传输前的一个时钟周期发生改变,这样可以使从属装置得到与被传输的串行数据同步的时间,并且使接收端存储当前的命令以及为下次的命令清除空间。

3、SD: (serial data) 串行数据

用二进制补码表示的音频数据。 I2S 格式的信号无论有多少位有效数据,数据的最高位总是被最先传输(在 WS 变化(也就是一帧开始)后的第 2 个 SCK 脉冲处),因此最高位拥有固定的位置,而最低位的位置则是依赖于数据的有效位数。也就使得接收端与发送端的有效位数可以不同。如果接收端能处理的有效位数少于发送端,可以放弃数据帧中多余的低位数据;如果接收端能处理的有效位数多于发送端,可以自行补足剩余的位(常补足为零)。这种同步机制使得数字音频设备的互连更加方便,而且不会造成数据错位。为了保证数字音频信号的正确传输,发送端和接收端应该采用相同的数据格式和长度。当然,对 I2S 格式来说数据长度可以不同。

对于系统而言,产生 SCK 和 WS 的信号端就是主设备,用 MASTER 表示,简单系统示意图如图 1所示:

另一个基本的接口时序图可以参看图 2 所示:

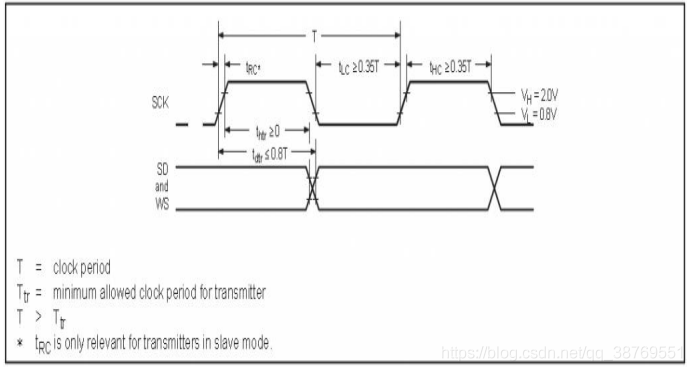

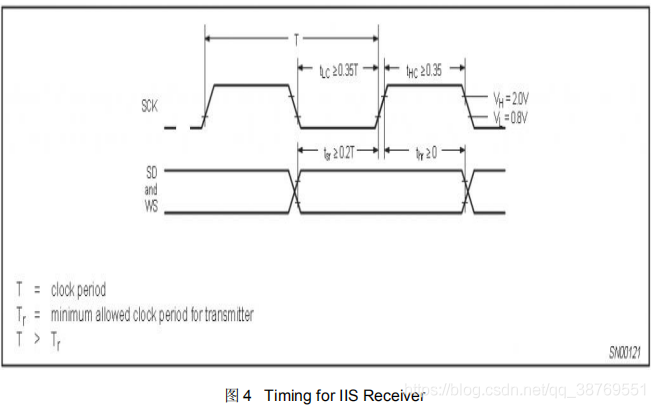

4、时序要求

在 IIS 总线中,任何设备都可以通过提供必需的时钟信号成为系统的主设备置,而从属设备通过外部时钟信号来得到它的内部时钟信号,这就意味着必须重视主设备和数据以及命令选择信号之间的传播延迟,总的延迟主要由两部分组成:

1.外部时钟和从设备的内部时钟之间的延迟

2.内部时钟和数据信号以及命令选择信号之间的延迟

对于数据和命令信号的输入,外部时钟和内部时的延迟不占据主导的地位,它只是延长了有效的建立时间(set-up time)。延迟的主要部分是发送端的传输延迟和设置接收端所需的时间。见图 3 和 图 4:

5、电气特性

输出电压:

VL <0.4V

VH>2.4V

输入电压

VIL=0.8V

VIH=2.0V

注:目前使用的 TTL 电平标准,随着其他 IC(LSI)的流行,其他电平也会支持。