ESP32-PICO-D4介绍与使用。

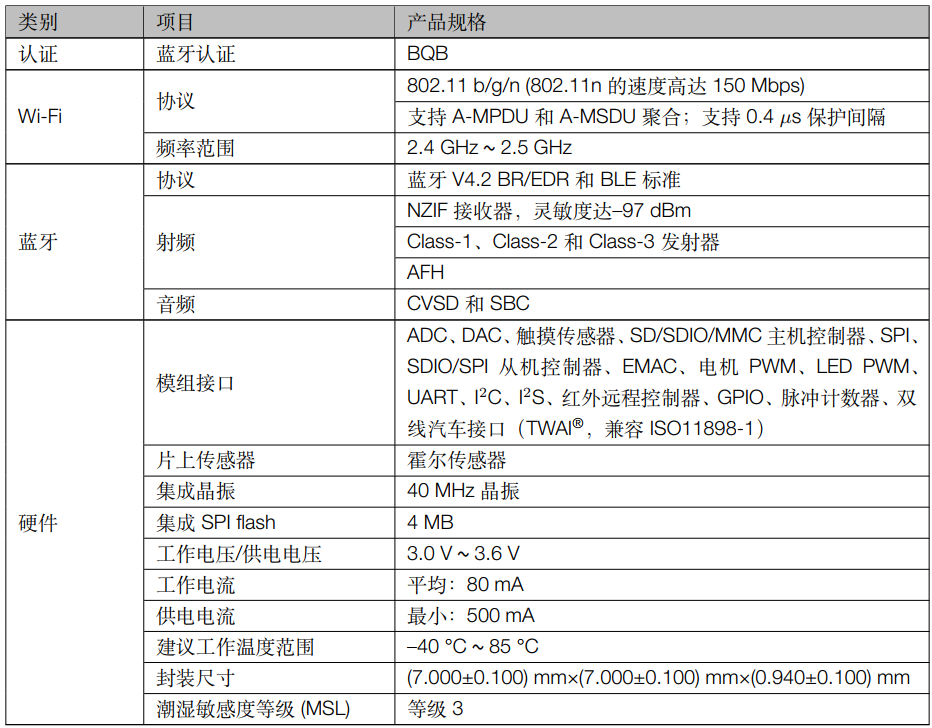

特点

尺寸仅为 (7.000±0.100) mm × (7.000±0.100) mm × (0.940±0.100) mm

集成1 个 4 MB 串行外围设备接口 (SPI) flash

集成 2.4 GHz Wi-Fi 和蓝牙双模的单芯片方案,采用台积电(TSMC) 超低功耗的 40 纳米工艺

已将晶振、 flash、滤波电容、 RF 匹配链路等所有外围器件无缝集成进封装内,不再需要外围元器件即可工作

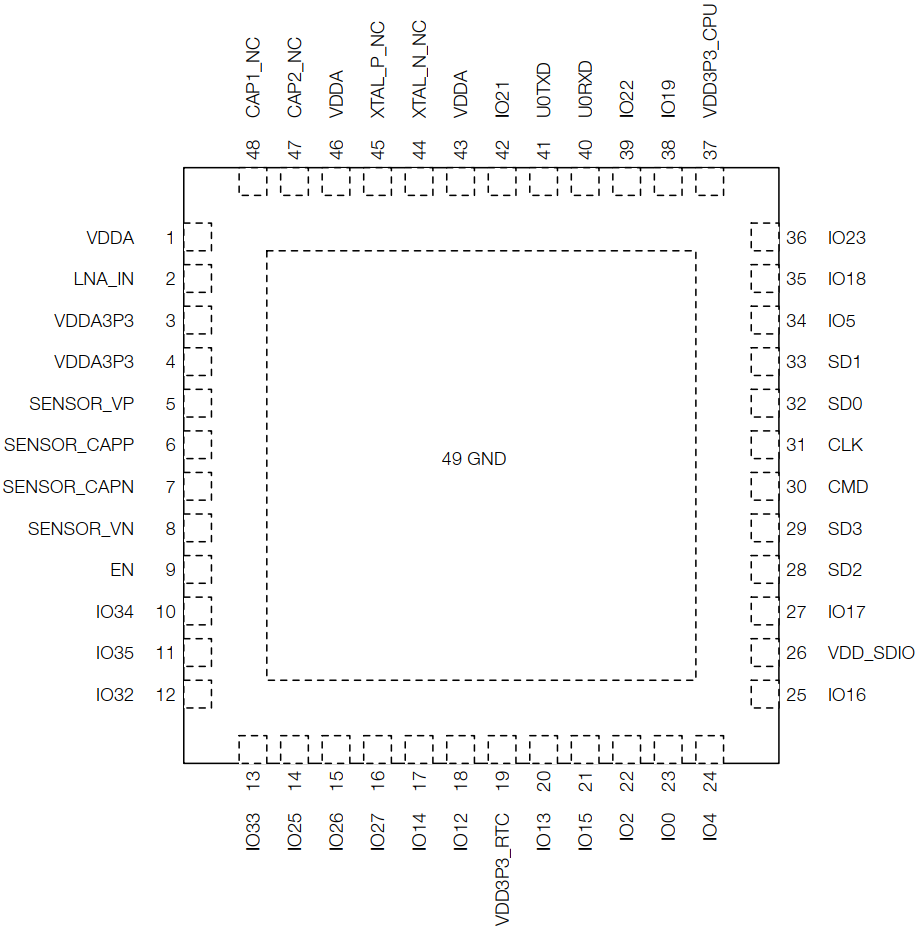

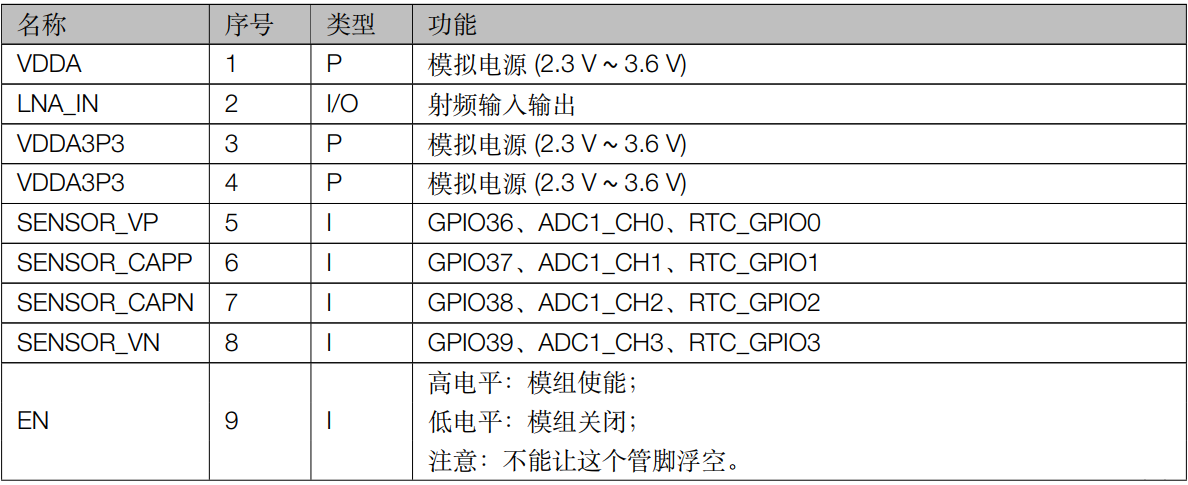

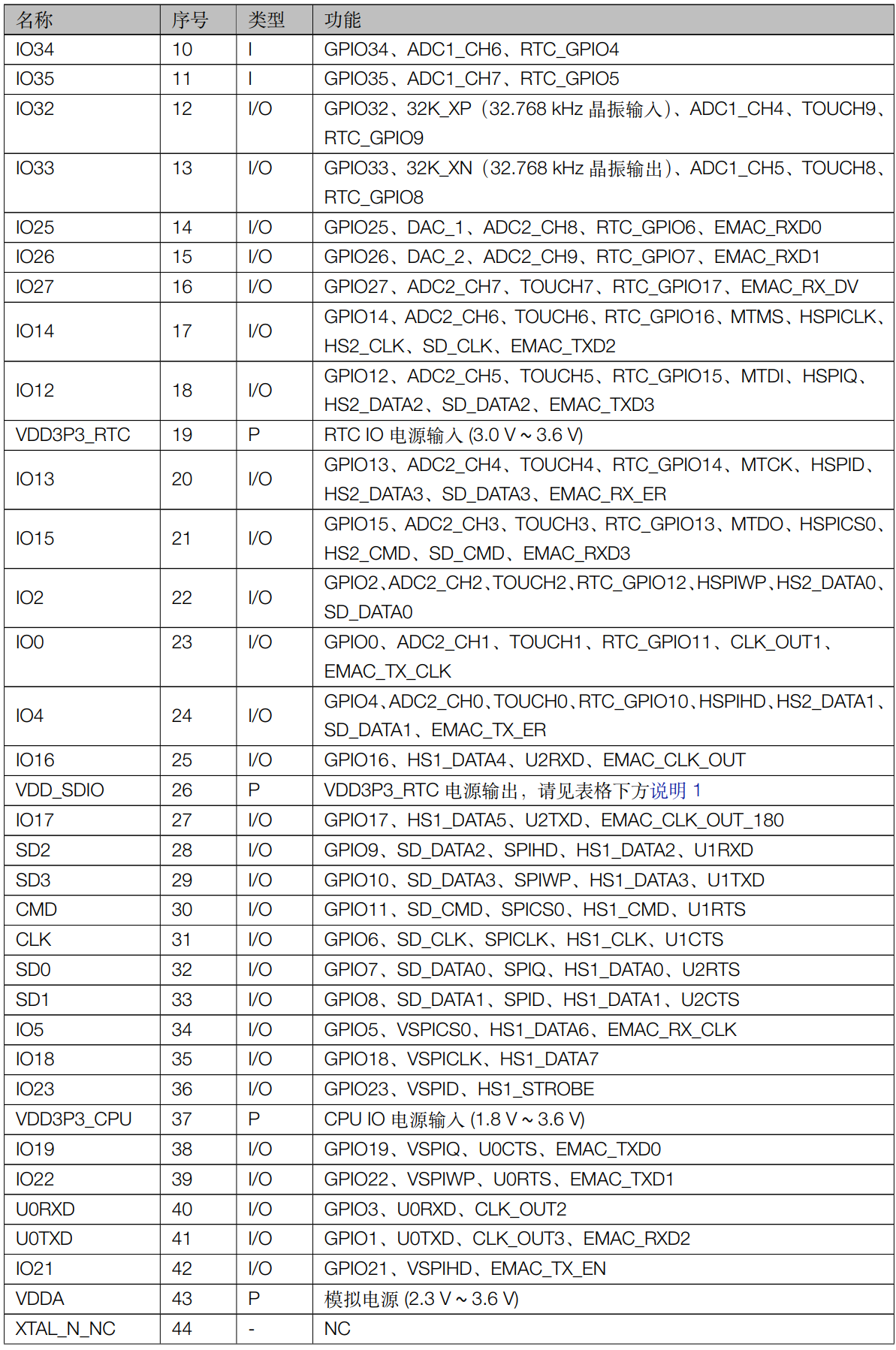

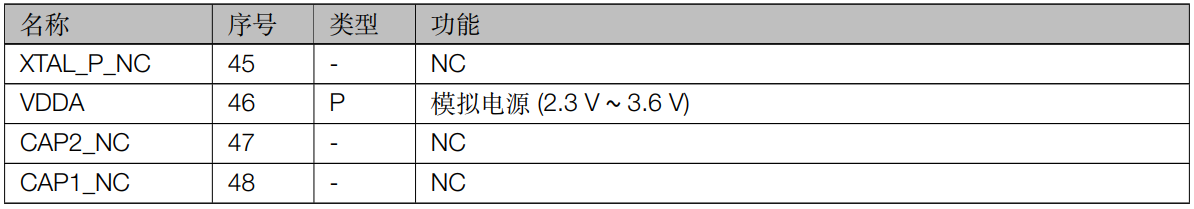

管脚

嵌入式 flash 连接至 VDD_SDIO(26脚),由 VDD3P3_RTC 通过约 6 Ω 电阻直接供电。因此, VDD_SDIO 相对 VDD3P3_RTC(19脚)会有一定电压降。 IO16(25脚)、 IO17(27脚)、 CMD(30脚)、 CLK(31脚)、 SD0(32脚) 和 SD1(33脚) 用于连接嵌入式 flash,不可用于其他功能。 如果要外接 PSRAM,推荐使用 SD3 (GPIO10) 用于 PSRAM_CS。 Strapping 管脚 ESP32 共有 5 个 Strapping 管脚:MTDI(18脚)、GPIO0(23脚)、GPIO2(22脚)、MTDO(21脚)、GPIO5(34脚)

描述

软件可以读取寄存器“GPIO_STRAPPING”中这 5 个管脚 strapping 的值。 在芯片的系统复位(上电复位、 RTC 看门狗复位、欠压复位)放开的过程中,Strapping 管脚对电平采样并存储到锁存器中,锁存为“0”或“1”,并一直保持到芯片掉电或关闭。 每一个 Strapping 管脚都会连接内部上拉/下拉。如果一个 Strapping 管脚没有外部连接或者连接的外部线路处于高阻抗状态,内部弱上拉/下拉将决定 Strapping 管脚输入电平的默认值。 为改变 Strapping 的值,用户可以应用外部下拉/上拉电阻,或者应用主机 MCU 的 GPIO 控制 ESP32 上电复位放开时的 Strapping 管脚电平。 复位放开后, Strapping 管脚和普通管脚功能相同。

功能

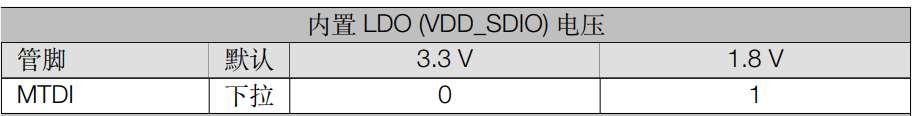

MTDI控制内置LDO的输出电压,VDD_SDIO(26脚)

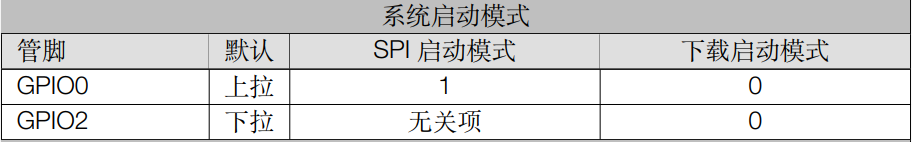

GPIO0、GPIO2控制启动模式,从内部的SPI Flash正常启动还是进入下载模式。

GPIO0、GPIO2控制启动模式,从内部的SPI Flash正常启动还是进入下载模式。

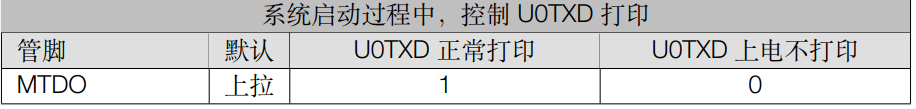

MTDO在系统启动过程中,控制 U0TXD 打印

MTDO在系统启动过程中,控制 U0TXD 打印

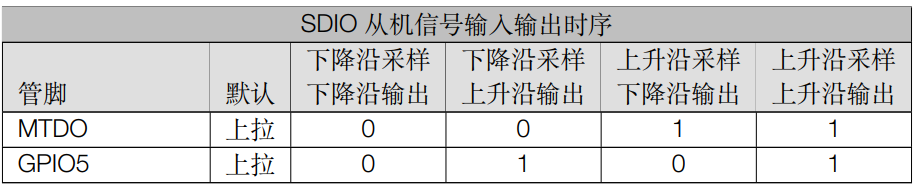

MTDO、GPIO5控制SDIO 从机信号输入输出时序

MTDO、GPIO5控制SDIO 从机信号输入输出时序

功能描述

CPU 和片上存储

ESP32-PICO-D4 搭载 2 个低功耗 Xtensa® 32-bit LX6 微处理器。

ESP32-PICO-D4 片上存储包括:

448 KB 的 ROM,用于程序启动和内核功能调用

用于数据和指令存储的 520 KB 片上 SRAM

RTC 快速存储器,为 8 KB 的 SRAM,可以在 Deep-sleep 模式下 RTC 启动时用于数据存储以及被主CPU 访问 RTC 慢速存储器,为 8 KB 的 SRAM,可以在 Deep-sleep 模式下被协处理器访问 1 Kbit 的 eFuse,其中 256 bit 为系统专用(MAC 地址和芯片设置) ; 其余 768 bit 保留给用户程序, 这些程序包括 flash 加密和芯片 ID

外部 Flash 和 SRAM

ESP32 支持多个外部 QSPI flash 和静态随机存储器 (SRAM)。详情可参考《ESP32 技术参考手册》 中的 SPI 章节。 ESP32 还支持基于 AES 的硬件加解密功能,从而保护开发者 flash 中的程序和数据。

ESP32 可通过高速缓存访问外部 QSPI flash 和 SRAM:

外部 flash 可以同时映射到 CPU 指令和只读数据空间。

当映射到 CPU 指令空间时,一次最多可映射 11 MB + 248 KB。如果一次映射超过 3 MB + 248 KB,则 cache 性能可能由于 CPU 的推测性读取而降低。

当映射到只读数据空间时,一次最多可以映射 4 MB。支持 8-bit、 16-bit 和 32-bit 读取。

外部 SRAM 可映射到 CPU 数据空间。一次最多可映射 4 MB。支持 8-bit、 16-bit 和 32-bit 访问。

ESP32-PICO-D4 集成了 4 MB 的外部 SPI flash。

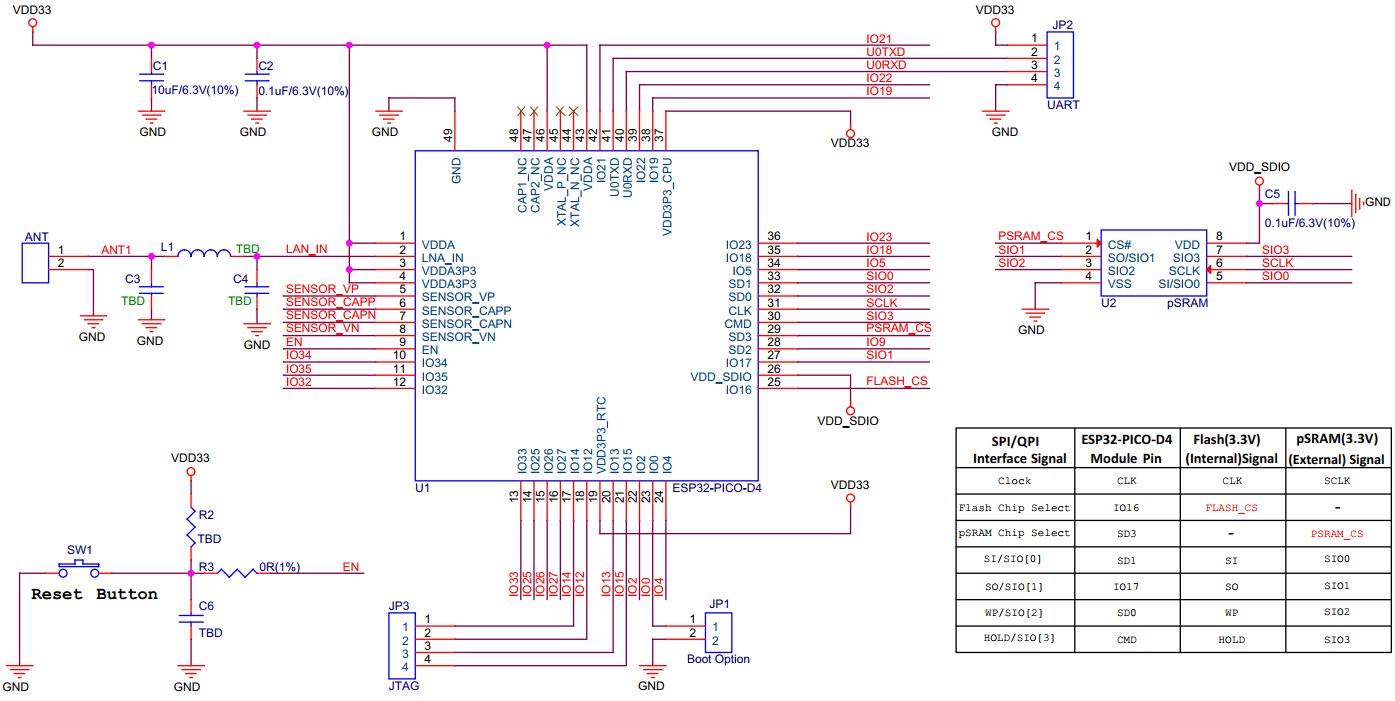

原理图